|

Двухканальный контроллер-коммутатор Ethernet KS8842

В статье приводится описание функций двухканального контроллера-коммутатора Ethernet KS8842. Потребность в таких микросхемах особенно остра в связи с появлением на рынке более производительных микроконтроллеров, а также в связи с ростом сети Ethernet.

Введение

Типовая структура устройства сопряжения с Ethernet может быть представлена следующей формулой:

PHY + MAC + CPU + RAM.

Здесь PHY — узел стыка с физической линией, MAC — контроллер МАС-адресов, CPU — микроконтроллер, RAM — память для накопления и хранения пакетов данных. Есть несколько вариантов выполнения устройств сопряжения. Традиционно контроллер и память выполнялись на отдельных от всего набора микросхемах. Узел стыка с физической линией (PHY, трансиверы) во многих применениях тоже выполнялся в виде отдельных микросхем. МАС-контроллеры обычно встроены как аппаратные узлы в микроконтроллеры, а теперь и в FPGA. Ранее МАС-контроллеры встраивались в FPGA как софт-ядра.

Слагаемые в приведенной выше формуле можно также рассмотреть по условию «инженерозависимости». Компоненты PHY, MAC и RAM не сильно зависят от участвующих в разработке инженеров, CPU же можно квалифицировать как «сильно инженерозависимый» компонент.

Опыт работы с определенным типом CPU, наличие библиотек из проверенных программных фрагментов кода, а также отладочных программных и аппаратных средств привязывают разработчиков к тем или иным видам микроконтроллеров. Переход на другой тип микропроцессора всегда связан с определенными трудностями. Именно поэтому получила распространение сокращенная версия приведенной выше формулы :

EthConr + CPU

Здесь EthConr = PHY + MAC +RAM — контроллер Ethernet.

Типичным представителем, получившим наиболее широкое применение для встроенных приложений, является микросхема CS8900, называемая «Highly-Integrated ISA Ethernet Controller». Данная микросхема подключается по параллельной шине к микроконтроллеру и снимает с разработчика необходимость решения проблемы Ethernet.

Однако с введением стандарта 100 Мбит/с данная микросхема катастрофически устарела. То же самое можно сказать и о ее параллельной шине. Асинхронная процессорная шина также безнадежно устарела и не может осуществлять обмен данными на высоких частотах. Чем же можно заменить Ethernet-контроллер, чтобы решить проблему Ethernet и плюс к этому иметь множество дополнительных функций, повышающих эксплуатационные характеристики изделия?

Для этого можно использовать KS8842M — двухканальный контроллер-коммутатор Ethernet фирмы Micrel [1].

KS8842 — первый взгляд

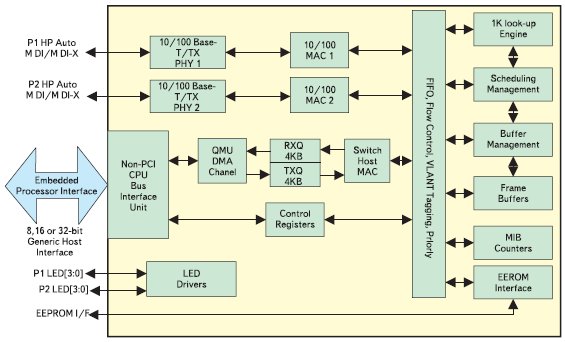

Блок-схема двухканального контроллеракоммутатора Ethernet приведена на рис. 1.

Рис. 1. Блок-схема микросхемы KS8842

На рисунке приведены основные узлы KS8842M:

- два малопотребляющих 10/100 приемопередатчика;

- два блока MAC;

- канал прямого доступа к памяти (DMA);

- высокоскоростной неблокирующий коммутатор;

- внутрикристальная память для таблицы обработки адресов (1 Кбайт);

- внутрикристальная память для буферов кадров данных;

- интерфейс с процессором разрядностью 8/16/32 бит, поддерживающий синхронные и асинхронные операции.

KS8842M может быть сконфигурирован как свитч или как репитер с низким временем ожидания ( 310 нс) для встроенных или индустриальных Ethernet-устройств. 310 нс) для встроенных или индустриальных Ethernet-устройств.

В интерфейсе Ethernet KS8842M имеет полный набор стандартных функций. Кроме того, KS8842M предлагает расширенный набор возможностей, который включает в себя:

- работу в виртуальной сети на основе тега или порта — tag/port-based VLAN;

- качество обслуживания (QoS) с приоритетным управлением;

- счетчики событий, основанные на информации (MIB);

- интерфейс управления и данных для центрального процессора, чтобы эффективно обрабатывать адреса для приложений Fast Ethernet.

Возможности микросхемы

- Управление коммутатором

- Неблокируемый коммутатор пакетов осуществляет быструю доставку пакетов, используя специальную таблицу переадресации пакетов.

- Полная совместимость со стандартом IEEE 802.3u.

- Управление потоком данных в режиме полного дуплекса IEEE 802.3x с возможностью использования режима «force».

- Управление потоком данных в режиме полудуплекс, режим обратного давления.

- Расширенное управление коммутатором

- Виртуальная сеть VLAN (IEEE 802.1Q) — поддерживается до 16 групп (полный диапазон VLAN-идентификаторов).

- VLAN-идентификатор на основе «tag/untag» виртуальной сети, связанной с определенным портом.

- Вставка или удаление тега в данных для виртуальной сети связанной с определенным портом по IEEE 802.1p/Q.

- Программируемое ограничение объема принимаемых и передаваемых данных для каждого порта.

- Защита от лавины широковещательных пакетов.

- Поддержка протокола «spanning tree» IEEE 802.1d.

- Функция фильтрации MAC, позволяющая отфильтровывать и не отправлять пакеты по неизвестным индивидуальным (unicast) адресам.

- Прямой режим «forward», дающий возможность процессору идентифицировать входной и выходной порты.

- Поддерживается протокол поиска по Internet Group Management Protocol (IGMP) v1/v2 для групповой фильтрации пакета.

- Поддерживается протокол поиска IPV6 Multicast Listener Discovery (MLD).

- Контроль принимаемой информации

- Для порта — отзеркаливание, мониторинг, пассивное прослушивание сети: входящий и исходящий трафик для любого порта.

- MIB-счетчики для сбора статистики (34 MIB-счетчика на порт).

- Режимы «Loopback» и диагностики отказа на дальнем конце линии.

- Доступ ко всем регистрам

- Управление оперативной перестройкой конфигурации через регистры (приоритет порта, 802.1p/d/Q).

Поддержка приоритетов QoS/CoS

- Основанная на порте, на IEEE 802.1p и DiffServ.

- Ремаппинг поля приоритетов по IEEE 802.1p для каждого порта.

- Режимы снижения потребляемой мощности, питание, температура, корпусировка

- Режим снижения мощности для всей микросхемы.

- Режим уменьшения потребляемой мощности на каждый порт PHY (обнаружение состояния линии «idle», конфигурация регистров сохраняется).

- Единственное напряжение 3,3 В.

- Коммерческий температурный диапазон 0...+70 °C.

- Промышленный температурный диапазон –40...+85 °C.

- Корпус PQFP с 128 входами (возможен выпуск в корпусах LQFP с 128 входами).

- Доступны в 16-битной версии для 8/16-битной шины данных и для 32-битной версии для 32-разрядной шины данных.

- Дополнительные возможности. Интегрированный коммутатор пакетов для Layer-2 дает следующие возможности:

- Режим репитера.

- Динамическая буферная схема памяти (необходима для приложений типа «Видео по IP», где флуктуация изображения недопустима).

- Коммутатор на 2 Ethernet-порта с переконфигурируемыми шинами для подключения к интерфейсу 8, 16 или 32-разрядного процессора хоста.

- Кабельная диагностика по технологии Micrel LinkMD позволяет диагностировать дефектные кабели и определить расстояние до дефекта.

- Автопереключение входов Tx-Rx по Hewlett Packard (HP) MDI-X с функцией запрета и разрешения позволяет упростить кабельный монтаж.

- Четыре приоритетных очереди для обработки пакетов с разным содержанием, например звука, видео, данных, а также управляющих пакетов.

- Способность передавать и получать кадры данных гигантского размера — до 1916 байт.

Сравнительные характеристики

Сравнительные характеристики микросхем приведены в таблице 1. В семейство Ethernet-контроллеров фирмы Micrel кроме контроллеров с выходом на процессорную шину общего назначения входят и Ethernet-контроллеры с выходом на шину PCI.

Таблица 1. Сравнительные характеристики микросхем Ethernet-контроллеров

| Фирма-производитель |

Micrel |

SMSC |

Cirrus |

Davicom |

RealTek |

| Название микросхемы |

KSZ8841-16MQL, KSZ8841-32MQL |

LAN91C111 |

CS8900A |

DM9000 |

RTL8019AS |

| Общие параметры |

|

|

|

|

|

| Промышленный температурный диапазон |

KS8841-16MVLI (Q1 — 2006) |

LAN91C111i |

CS8900A-IQ (5V)

CS8900A-IQ3 (3.3V) |

x |

x |

| Фирма также поставляет микросхемы 10/100 switch |

+ |

x |

x |

x |

+ |

| PHY |

|

|

|

|

|

| Скорость PHY |

10/100 |

10/100 |

10 |

10/100 |

10 |

| Автопереговоры |

+ |

+ |

x |

+ |

x |

| HP Auto-MDIX Crossover |

+ |

x |

x |

x |

x |

| Wake up on LAN |

PowerSave |

x |

+ |

+ |

|

| Конфигурация |

|

|

|

|

|

| Диагностика медного кабеля |

LinkMD |

x |

x |

x |

x |

| Доступ к EEPROM |

EEPROM чтение-запись |

EEPROM запись |

EEPROM запись |

EEPROM запись |

|

| Шина/ МАС/SWITCH |

|

|

|

|

|

| Размер буфера |

8KB w/4B dynamic allocation |

allocation8KB w/ fixed 2KB allocation |

4KB |

3KB TX/13KB RX Only 2 TX packets can be stored |

16KB |

| Шина 8/16/32 разряда |

+ |

+ |

Только 16 разрядов |

+ |

+ |

| Тактовая частота (скорость передачи данных) |

50 МГц |

|

8–11 МГц |

|

|

| PCI NIC CONTROLLER KSZ8841PMQL [Q3 RELEASE] |

KS8841PMQL |

x |

x |

DM9102C |

RTL8100BL, RTL8139CL/DL |

| PCI + SWITCH/Repeater KSZ8842PMQL [Q3 RELEASE] |

KS8842PMQL |

x |

x |

x |

x |

Приложения для применения

- Сетевые видеосистемы.

- Высокопроизводительные кабельные, спутниковые и телевизионные приставки с выходом в Интернет.

- Видео по IP.

- Голос по IP (VoIP) и аналоговые телефонные адаптеры (ATA).

- Промышленные системы управления и контроля, чувствительные ко времени выполнения.

- Управление двигателями.

- Промышленные устройства контроля с датчиками (температура, давление, уровни, клапаны).

- Охранные системы и камеры наблюдения.

Функциональный краткий обзор

Описание «трансиверной» части микросхемы

«Трансиверная» часть микросхемы выполнена совершенно стандартно, как и у обычных трансиверов, кроме двух моментов, о которых необходимо сказать отдельно, — это автопереключение входов MDI–MDI-X и диагностика кабеля по технологии LinkMD.

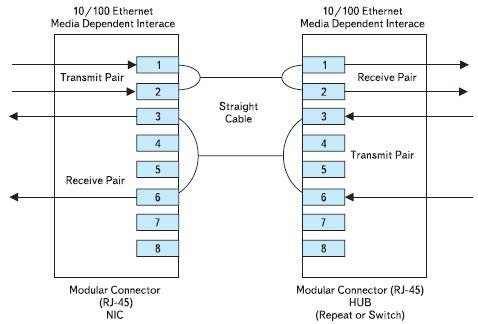

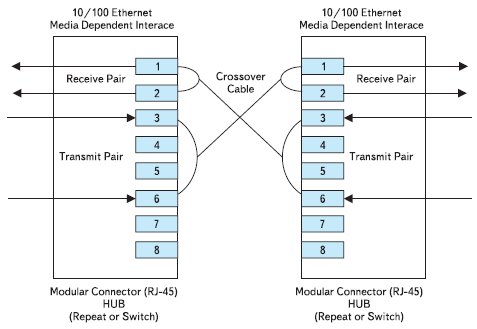

Автопереключение входов MDI–MDI-X

Автопереключение входов Tx-Rx по Hewlett Packard MDI-X с функцией запрета и разрешения позволяет упростить кабельный монтаж. В таблице 2 приведено распределение сигналов по контактам в разъеме при прямом и перекрестном соединении. На рис. 2–3 приведена схема кабеля для соединения двух устройств при прямом и перекрестном соединении.

Рис. 2. Схема кабеля (прямое соединение)

Рис. 3. Схема кабеля (перекрестное соединение)

Таблица 2. Расположение сигналов по контактам в разъеме при прямом и перекрестном соединении

| MDI |

MDI-X |

| Контакты RJ45 |

Сигналы |

Контакты RJ45 |

Сигналы |

| 1 |

TD+ |

1 |

RD+ |

| 2 |

TD– |

2 |

RD– |

| 3 |

RD+ |

3 |

TD+ |

| 6 |

RD– |

6 |

TD– |

Входная часть микросхемы может определить, подключена ли она к выходу передатчика. Если определение происходит успешно, то принимается текущее расположение входов и выходов. В том случае, если определение не происходит успешно, то производится попытка определить расположение выводов при перекрестном соединении. Если определяется перекрестное соединение, то оно принимается за рабочее.

Это позволяет соединять устройства независимо от того, как выполнено другое устройство и какой тип кабеля (прямой или перекрестный) применяется. Данная функция может быть программно разрешена или запрещена, что выполняется записью соответствующих кодов в регистры управления.

Кабельная диагностика по LinkMD

KS8842M LinkMD использует технологию Time domain reflectometry (TDR) для определения таких обычных для кабелей отказов, как обрывы в линии, короткие замыкания и несоответствие импеданса.

LinkMD работает следующим образом: в линию посылается импульс известной амплитуды и продолжительности, и затем производится анализ формы отраженного сигнала. Положение отраженного импульса относительно посылаемого, а также его продолжительность позволяют определить расстояние до аварии в кабеле. Максимальное расстояние — до 200 м с точностью ±2 м. Внутренняя схема отображает информацию от TDR в удобочитаемом для пользователя цифровом формате. (Кабельная диагностика работает только для медных подключений, операции с оптоволокном не поддерживаются.)

MAC и коммутатор

Наиболее сложная часть микросхемы — МАС и коммутатор. Именно эти узлы и повышают производительность микросхемы по сравнению с обычным вариантом МАС + CPU. Поскольку все перечисленные здесь основные и дополнительные функции выполняются аппаратно, не требуя ресурса от CPU, то это позволяет значительно упростить разработку устройства в целом.

Поиск MAC-адреса

Внутренняя поисковая таблица хранит MAC-адреса и связанную с ними информацию. Она состоит из таблицы выделенных одноадресных пакетов и данных для коммутатора.

Изучение поступающих из линии адресов Внутренний механизм поиска дополняет таблицу адресов новым адресом из пакета, если выполнены следующие условия:

- В полученном пакете адрес отправителя Source Address (SA) не существует в поисковой таблице.

- Полученный пакет имеет признаки правильного пакета, то есть не были получены ошибки при приеме, размер пакета имеет правильную длину.

Механизм поиска вставляет новый SA в таблицу наряду с номером порта и временной меткой. Если таблица заполнена, последняя запись в таблице удаляется, чтобы создать место для новой записи.

Перемещение устройства

Внутренний механизм поиска также контролирует, изменялось ли местоположение станции. Если абонентов станции перекоммутировали относительно, то необходимо обновить таблицу адресов. Перемещение происходит, когда выполнены следующие условия:

- SA полученного пакета находится в таблице, но связанная с ним исходная информация о порте отличается от той, что пришла в пакете.

- Полученный пакет имеет признаки правильного пакета, не были получены ошибки при приеме, и размер пакета имеет правильную длину.

Механизм поиска обновляет существующую запись в таблице новой информацией о порте.

Старение таблицы

Механизм поиска обновляет информацию временной метки записи в таблице всякий раз, когда появляется передача SA. Временная метка используется в процессе старения. Если отчет не модифицирован на данный момент, то механизм поиска удаляет запись из таблицы.

Механизм поиска постоянно работает, производя обновление записей в таблице и удаляя устаревшие записи. Период старенияприблизительно 200 с. Этот параметр можно разрешить или заблокировать в программно доступных регистрах управления.

Форвардинг пакетов

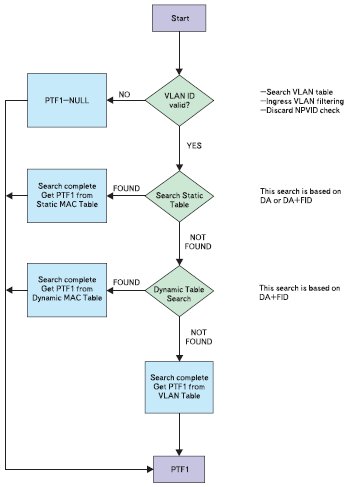

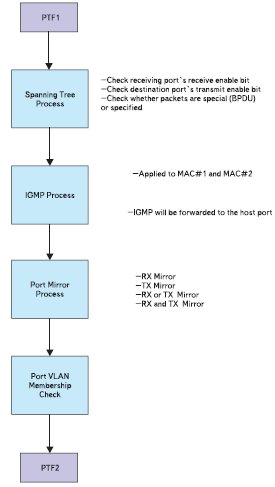

Пакеты перенаправляются по алгоритму, который изображен на блок-схемах рис. 4, 5.

Рис. 4. Блок-схема алгоритма поиска по таблице адреса для определения адреса назначения пакета (стадия 1)

Рис. 5. Блок-схема алгоритма поиска по таблице адреса для определения адреса назначения пакета (стадия 2)

На рис. 4 показано, как выполняется первый шаг алгоритма отправки пакета, где поисковый сервер ищет VLAN-идентификатор, статическую таблицу и динамическую таблицу для адреса назначения, приходя к состоянию «порт для отправки 1» (PTF1). Затем адрес назначения PTF1 изменяется в соответствии со «spanning tree», с пассивным прослушиванием сети (IGMP), с зеркальным отражением порта и с VLAN так, чтобы прийти к состоянию «порт для отправки 2» (PTF2), как показано на рис. 5. В результате пакет посылают по адресу PTF2.

KS8842M не будет отправлять следующие пакеты:

- Пакеты с ошибками. Пакеты имеют ошибки кадровой синхронизации, ошибки в Frame Check Sequence (FCS), ошибки в расположении данных ошибки, а также ошибки, связанные с неправильной длиной пакета.

- Кадры паузы IEEE 802.3x. KS8842M прерывает эти пакеты и выдает пакеты управления потоком данных.

- «Местные» пакеты. Производится поиск по адресу назначения (DA). Если порт адресата из поисковой таблицы соответствует порту, от которого исходит пакет, пакет будет определен как «местный».

Механизм коммутации

KS8842M показывает высокую эффективность примененного механизма коммутации, который пересылает данные в буфер памяти пакетов MAC (или из него). Он работает в режиме сохранения пакетов и в режиме форвардинга пакетов, что уменьшает полное время ожидания при передаче пакетов. Механизм коммутации имеет внутренний буфер объемом в 32 Кбайт. Этот ресурс разделен между всеми портами. Всего есть 256 доступных буферов по 128 байт.

Операции МАС

KS8842M полностью соответствует стандарту IEEE 802.3. Кроме того, в МАС есть функция фильтрации одноадресных пакетов. Эта функция полезна в приложениях типа VoIP, где ограничение на обработку некоторых пакетов уменьшает нагрузку и таким образом улучшает работу.

Промежуток между пакетами (IPG)

Если кадр данных успешно передан, то после этого между двумя последовательными пакетами передается пауза— IPG, имеющая длительность как минимум 96 бит временных тактов. Если линия связи работает в режиме полудуплекса, то в линии возможны столкновения данных, в том случае, если два абонента линии начали одновременно передавать данные. В таком случае, перед началом следующей передачи, KS8842M выполнит паузу длительностью не менее чем 96 временных тактов для паузы между пакетами (IFG) от момента определения несущей частоты (CRS) .

Алгоритм выдержки паузы

KS8842M осуществляет стандартный алгоритм по IEEE 802.3 для выдержки паузы в режиме полудуплекса и, кроме того, «агрессивный режим» выдержки. После 16 столкновений пакет, возможно, будет выброшен (в зависимости от конфигурации коммутатора, установленной в программно-управляемом регистре управления).

Позднее столкновение данных в линии

Если переданный пакет испытывает коллизии после 512 временных тактов передачи, он будет выброшен.

Правильный размер пакета

KS8842M не принимает пакеты, длительность которых меньше чем 64 байта, и может быть запрограммирован так, чтобы принять пакет длиной до 1536 байт. KS8842M может также быть запрограммирован для получения пакетов длиной до 1916 байт.

Управление потоком данных

KS8842M поддерживает стандарт 802.3x при управлении потоком данных как на стороне передачи, так и на стороне приема. На приемной стороне, если KS8842M получает управляющий пакет с паузой, то следующий нормальный кадр данных передаваться не будет до истечения времени таймера, указанного в пакете управления длительностью паузы.

Если будет получен другой управляющий пакет с паузой до истечения времени, таймер будет модифицирован с новым значением для второй паузы. В течение этого периода (так как имеет место поток управления), от KS8842M будут передаваться только управляющие пакеты.

На передающей стороне KS8842M может решать, когда вызвать управление потоком данных. Управление потоком данных основано на доступности системных ресурсов, включая буфера, очереди для передачи и очереди для приема.

KS8842M будет управлять потоком данных для того порта, который только что получил пакет, если ресурс порта адресата занят. KS8842M выпускает кадр для управления потоком данных — (Xoff), содержащий максимальное время паузы, определенное в стандарте IEEE 802.3x.

Как только ресурс будет освобожден, KS8842M отсылает другой кадр данных для управления потоком данных (Xon) с нулевым временем паузы, чтобы выключить управление потоком данных (включение передачи к порту). Управление имеет вид гистерезиса для предотвращения постоянного включения и выключения механизма управления потоком данных.

KS8842M производит управление потоком данных для всех портов, если принимаемая очередь заполняется данными.

Сокращение потока принимаемых пакетов, выполняемое в режиме полудуплекса

Чтобы сократить число принимаемых пакетов KS8842M может выполнять так называемое противодавление, для этого KS8842M посылает преамбулы в линию, это вызывает коллизии и, следовательно, задерживает передачу других станций (этот режим работы не является необходимым требованием стандарта IEEE 802.3). В режиме дуплекса так же можно производить активацию и дезактивацию этого режима путем записи битов управления в программно управляемые регистры.

Защита от лавины широковещательных пакетов

KS8842M имеет возможность защиты коммутатора от получения и рассылки слишком большого числа широковещательных пакетов. Поскольку широковещательные пакеты направляются всем портам кроме исходного, имеет место чрезмерный рост числа занятых ресурсов коммутатора (полоса пропускания и доступное пространство в очередях на передачу).

KS8842M имеет возможность включить «групповые пакеты» в режим ограничения по рассылке в случае «штормового» режима управления. Параметры нормы при возникновении лавины широковещательных пакетов запрограммированы глобально, и их можно разрешить или заблокировать для каждого порта отдельно.

Норма времени — 67 мс для 100 Bт и 670 мс для 10 Bт. В начале каждого интервала счетчик очищается, чтобы начать заново считать число байтов. По умолчанию этот параметр устанавливается равным 0х63 (99 в десятичной системе). Это соответствует значению 1% от нормы и рассчитывается следующим образом:

148 800 кадров данных/с x 67 мс/интервалов | 1% = 99 кадров данных/интервалов (приблизительно) = 0x63

Заметим, что число 148 800 кадров данных/с получено исходя из того, что длина блока данных в пакете равна 64 байта в 100Base-T с 12 байт паузы IPG и 8 байт преамбулы между двумя пакетами.

Генератор синхрочастоты

Входы микросхемы X1 и X2 связаны с кварцем 25 МГц.

Блок интерфейса с магистралью (BIU) использует BCLK (синхрочастота шины) для синхронных операций по шине. Максимальная частота порта хоста — 50 МГц для VLBUS-подобного интерфейса, работающего в режиме burst (только для 32-разрядных интерфейсов).

Блок интерфейса с магистралью (Bus Interface Unit — BIU)

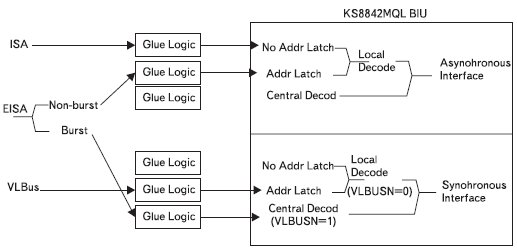

Интерфейс хоста (BIU) разработан для связи со встроенными процессорами. Интерфейс хоста KS8842M — универсальный шинный интерфейс. Когда интерфейс стыкуется с различными шинами и процессорами, может потребоваться немного согласующей логики.

На стороне передачи BIU может поддержать два режима передачи: асинхронный и синхронный. Для работы в этих режимах BIU имеет три группы сигналов:

- Синхронные сигналы.

- Асинхронные сигналы.

- Общие сигналы (используются и для синхронных, и для асинхронных передач).

Поскольку и синхронные, и асинхронные сигналы независимы друг от друга, синхронная передача типа burst и асинхронная передача могут быть смешаны или чередоваться, но им нельзя перекрываться (из-за совместного использования общих сигналов).

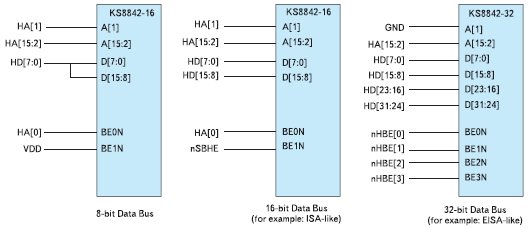

KS8842M поддерживает размер шины данных в 8, 16 и 32 бита.

Для 32-разрядной шины данных системы или хоста могут быть произведены 8, 16 и 32-разрядные передачи данных (KS8842-32), для 16-разрядной шины данных — 8 и 16-разрядные (KS8842-16), а для шины данных 8 бит будет возможна передача только в 8 бит (KS8842-8).

Независимо от того, является ли передача синхронной или асинхронной, если требуется защелка адреса, то используют задний фронт ADSN для того, чтобы защелкнуть приходящее значение сигналов на линиях А[15:1], AEN, BE3N, BE2N, BE1N и BE0N.

Асинхронный интерфейс

Для асинхронных передач имеются асинхронные выделенные сигналы RDN (для чтения) и WRN (для записи), и они переключаются в то время, как синхронные выделенные сигналы CYCLEN, SWR и RDYRTNN сброшены и остаются на одном логическом уровне в течение всех циклов асинхронной передачи.

Для асинхронной передачи данных нет поддержки режима burst. Все асинхронные передачи являются только передачей одного слова данных. Блок сопряжения BIU, однако, обеспечивает гибкую асинхронную связь с помощью интерфейса. Есть три основных способа подключения интерфейса с хосту.

- Связь с хостом по интерфейсу, основанному на локальном декодировании адреса устройства. В состав интерфейса входят шины адреса, на которых во время всего цикла обмена установлены достоверные значения адреса.

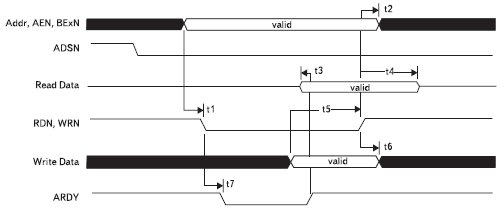

Типичный пример для этого применения — ISA-подобный шинный интерфейс, использующий предварительно защелкнутые сигналы адреса (рис. 6). Не требуется никакой дополнительный фиксатор адреса, поэтому ADSN должен быть установлен в состояние низкого уровня. Блок BIU декодирует сигналы адреса А[15:4] и объединяет эти сигналы с AEN (Address Enable), чтобы определить, является ли коммутатор KS8842M адресом назначения для этой операции. Хост использует задний фронт сигнала RDN, чтобы защелкнуть данные на чтение, и блок сопряжения с буфером будет использовать задний фронт сигнала WRN, чтобы защелкнуть данные на запись.

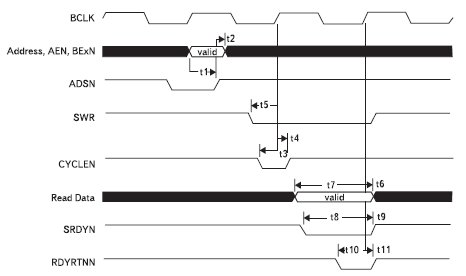

Рис. 6. Диаграмма процедуры асинхронного чтения. Во время цикла обмена данными имеется состояние достоверного и устойчивого адреса. Местное декодирование сигналов адреса

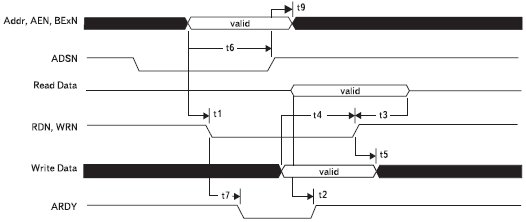

- Связь с хостом по интерфейсу, основанному на локальном декодировании адреса устройства. В состав интерфейса входят шины адреса, на которых достоверные значения адреса присутствуют только часть времени цикла обмена. Типичный пример - EISA-подобная шина (non-burst) (рис. 7).

Рис. 7. Диаграмма процедуры асинхронного чтения. Во время цикла обмена данными достоверные значения адреса присутствуют только часть времени цикла обмена. Местное декодирование сигналов адреса

Этот тип интерфейса требует, чтобы адрес был защелкнут на восходящем фронте сигнала ADSN. Блок BIU декодирует защелкнутые сигналы адреса А[15:4] и объединяет эти сигналы с AEN, чтобы определить, является ли коммутатор KS8842M адресом назначения для этой операции. Передача данных происходит так же, как и в первом случае.

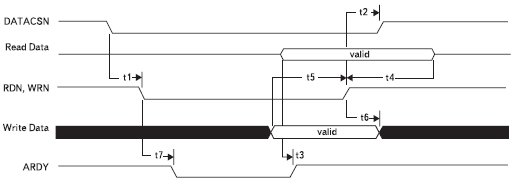

- Связь с помощью интерфейса с хостом, основанная на центральном декодировании устройства (режим применяется только для KS8842-32). Типичный пример этого применения — для встроенного процессора, имеющего центральный декодер на системной плате или внутри микросхемы процессора.

Соединение сигнала выбора чипа (CS) от системы или хоста с DATACSN обходит местный декодер адреса устройства. Когда DATACSN установлен, то только он разрешает доступ к 32-битному регистру данных, а сигналы BE3N, BE2N, BE1N и BE0N игнорируются, как показано на рис. 8. При этом невозможно обратиться к каким-либо другим регистрам. Передача данных та же самая, что и в первом случае. Чтобы вставить цикл ожидания, блок BIU устанавливает ARDY, продлевая таким образом цикл обмена.

Рис. 8. Диаграмма процедуры асинхронного чтения. Централизованное декодирование сигналов адреса

Синхронный интерфейс

Для синхронных передач управление обменом данными идет по синхронным выделенным сигналам CYCLEN, SWR и RDYRTNN, которые переключаются, а асинхронные выделенные сигналы RDN и WRN находятся на неактивном высоком уровне все время, пока идет синхронная передача данных.

Синхронный интерфейс главным образом поддерживается для двух приложений — одно для VLBUS-подобного, другое — для EISA-подобного (прямой доступ в память — DMA типа C), передачи типа burst. VLBUS-подобный интерфейс поддерживает только единственную передачу данных. Состояние входного контакта микросхемы VLBUSN определяет, будет ли микросхема работать в режиме burst как VLBUS-подобный интерфейс или как EISA-подобный интерфейс. Если VLBUSN = 0, то выбран интерфейс для VLBUS-подобной передачи, а если VLBUSN = 1, то выбран интерфейс для EISA-подобной передачи.

Для VLBUS-подобного интерфейса передачи (VLBUSN = 0)

Этот интерфейс применяется в архитектуре, в которой используется местный декодер адреса устройства; то есть блок BIU декодирует, защелкивает А[15:4] и объединяет эти сигналы с AEN (Address Enable), чтобы определить, является ли коммутатор адресатом для этой операции. В этом применении передачи типа burst не поддерживаются. Подключение сигнала M/nIO в VLBus направлено к AEN. CYCLEN в этом применении используется для того, чтобы произвести выборку сигнала SWR, когда тот установлен.

Обычно CYCLEN формируется из сигнала ADSN, задержанного на один такт синхрочастоты. Есть процесс процедуры установления связи и окончания циклов для VLBUS-подобных передач. Когда KS8842M готов закончить цикл, он устанавливает SRDYN.

Система или хост опознает SRDYN, устанавливая RDYRTNN после того, как защелкнуты данные на чтение. KS8842M держит данные на чтение до тех пор, пока не установлен RDYRTNN. Форма сигналов синхронизации показана на рис. 9.

Рис. 9. Диаграмма процедуры синхронного чтения. Местное декодирование сигналов адреса

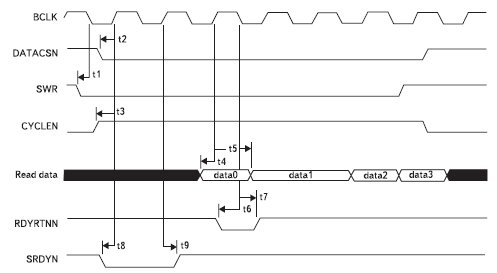

Для EISA-подобного интерфейса передачи (VLBUSN = 1)

Чтобы выполнить операцию шины burst-чтение, сигнал SWR связывается с IORC# в EISA, а чтобы выполнить операцию шины burst-запись, CYCLEN связывается с IOWC# в EISA. Обратите внимание, что в этом применении и система/хост/память, и KS8842M способны к вставке циклов ожидания. Если хост или память требуют циклов ожидания шины, то для этого должен быть использован сигнал RDYRTNN. Если для KS8842M требуется цикл ожидания шины, то устанавливается сигнал SRDYN. Форма сигналов синхронизации показана на рис. 10.

Рис. 10. Диаграмма процедуры синхронной шины — burst-чтение

Резюме

На рис. 11 показана организация сопряжения микросхемы KS8842 с интерфейсами различных типов, такими как ISA-подобные, EISA-подобные и VLBUS-подобные. На рис. 12 показано подключение микросхемы KS8842 к интерфейсам с различными размерами шины данных.

Рис. 11. Организация сопряжения микросхемы KS8842 с интерфейсами различных типов

Рис. 12. Подключение микросхемы KS8842 к интерфейсам с различными размерами шины данных

Для режима шины данных 8 бит между сигналами BE0N и BE1N может быть включен инвертор, так что четный адрес позволит работать сигналу BE0N, а нечетный — BE1N.

Блок управления очередями (QMU)

Блок управления очередями (Queue Management Unit — QMU) управляет трафиком пакетов между интерфейсом MAC/PHY и системным хостом. Он имеет встроенную память для функций приема и передачи пакетов, называемую RXQ (Receive Queue) и TXQ (Transmit Queue).

Каждая очередь содержит 4 Кбайт памяти для неблокирующего размещения пакетов данных в соседних блоках памяти. Это обеспечивается группой управляющих регистров, которые доступны для системного управления, кроме того, сюда относятся регистры состояния кадра данных для текущего передаваемого или получаемого пакета и регистры прерывания, которые служат для того, чтобы сообщить хосту состояние реального времени по TX/RX.

Формат кадра данных очереди на передачу (TXQ)

Формат кадра данных для очереди на передачу показан в таблице 3.

Таблица 3. Формат кадра данных для очереди на передачу

| Смещение адреса в памяти для размещения пакетов |

Бит 15 Бит 0

Байт 2 Байт 1 |

| 0 |

Control Word |

| 2 |

Byte Count |

| 4 — до конца пакета |

Данные пакета (до 1916) |

Первое слово содержит управляющую информацию для кадра данных на передачу. Второе слово используется для того, чтобы определить общее количество байтов кадра данных. Далее следуют данные пакета. Область данных пакета содержит непосредственно данные кадра. Эти данные могут включать в себя контрольную сумму (CRC) или не включать, в зависимости от того, какому аппаратному ресурсу разрешено генерировать контрольные суммы.

Множество кадров данных может быть помещено как в очередь на передачу, так и в очередь на прием — до тех пор, пока достаточно памяти для размещения очереди без переполнения. Для каждого переданного кадра данных информация о состоянии расположена в регистре TXSR.

Поддержка IGMP

Для поддержки уровня Layer 2 в Internet Group Management Protocol (IGMP) KS8842M обеспечивает два компонента:

«IGMP» Snooping

KS8842M принимает IGMP пакеты и отправляет их только на процессор (порт хоста).

IGMP-пакеты идентифицируются как пакеты IP (или пакеты IP Ethernet, или пакеты IEEE 802.3 SNAP IP) с версией IP = 0x4 и номером версии протокола = 0x2.

Вставка группового адреса в статической MAC-таблице

Как только групповой адрес занесен в статическую МАС-таблицу, он будет использоваться вместо широковещательных адресов.

Пассивное прослушивание линии MLD по IPv6 KS8842M принимает пакеты IPv6 Multicast Listener Discovery (MLD) и отправляет их только на процессор (порт хоста).

Поддержка режима отзеркаливания данных для порта

KS8842M поддерживает «зеркальное отражение данных порта» в следующих режимах:

Отзеркаливание данных порта для режима «только прием»

Все пакеты, полученные на порте, отражаются также на порте прослушивателя линии. Например, порт 1 запрограммирован быть «портом, от которого получают принимаемые данные», а порт хоста — «порт прослушивателя линии». Например, пакет, полученный на порт 1, после внутреннего поиска в таблице адресов предназначен для передачи на порт 2. KS8842M направит пакет и к порту 2, и к порту хоста. KS8842M может опционально даже отправить «плохо» полученные пакеты к «порту прослушивателя линии».

Отзеркаливание данных порта для режима «только передача»

Все пакеты, предназначенные для передачи в порте, отражаются также на порт прослушивателя линии. Например, порт 1 запрограммирован быть «портом, от которого получают передаваемые данные», а порт хоста — «порт прослушивателя линии». Пакет, полученный на порт 2, после внутреннего поиска в таблице адресов предназначен для передачи на порт 1. KS8842M направит пакет и к порту 1, и к порту хоста.

Отзеркаливание данных двух портов для режимов «прием и передача»

Все пакеты, полученные в порте А и переданные в порте B, отражаются на порт прослушивателя линии. Например, порт 1 запрограммирован быть «портом, который прослушивается», порт 2 — «портом, который прослушивается», а порт хоста — «портом прослушивателя линии». Пакет, полученный на порт 1, после внутреннего поиска в таблице адресов предназначен для передачи на порт 2, и, таким образом, KS8842M отправит пакет и к порту 2, и к порту хоста.

Несколько портов может быть выбрано как на приеме, так и на передаче в качестве «порта, который прослушивается». Кроме того, любой порт может быть отобран как «порт прослушивателя линии».

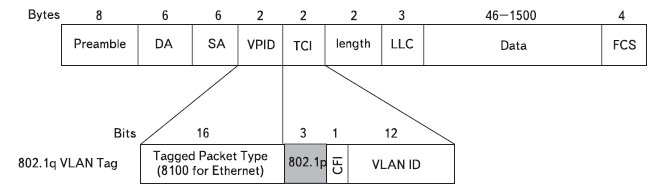

Поддержка виртуальной сети VLAN по IEEE 802.1Q

KS8842M поддерживает 16 активных виртуальных сетей VLAN из 4096 возможных, указанных в спецификации IEEE 802.1Q (рис. 13).

Рис. 13. Формат поля приоритетов по 802.1р

KS8842M имеет таблицу VLAN с 16 входами, которая конвертирует 12-битный идентификатор (VID) к 4-битному идентификатору Filter ID (FID) для поиска адреса. Если получен пакет с неотмеченным значением или со значением VID, равным нулю, то для поиска используется входное значение порта VID, установленное по умолчанию.

В режиме VLAN процесс поиска начинается с поиска в таблице значения VLAN, чтобы определить, получен ли достоверный VID.

Если VID не достоверный, то пакет выбрасывается, и его адрес не изучается для обновления таблицы адресов. Если VID достоверный, то идентификатор FID используется для дальнейшего поиска. Идентификатор файла + адрес назначения (FID+DA) используется, чтобы определить порт адресата. Идентификатор файла + исходный адрес (FID+SA) используется для изучения адреса.

Поддержка приоритетов — QoS

KS8842M обеспечивает стандарт «качество обслуживания» — Quality of Service (QoS) для приложении типа VoIP и видеоконференций. Для каждого порта имеется возможность передавать данные в соответствии с их приоритетом. Таким образом, формируются 4 приоритетных очереди: очередь 3— самая высокоприоритетная очередь, очередь 0— самая низкоприоритетная.

Приоритет по порту

Каждый входной порт определен как порт, имеющий высокий приоритет. Все пакеты, получаемые в таком входном порте, отмечаются как пакеты, имеющие высокий приоритет. Далее эти пакеты направляются в порт передачи и, если, очередь на передачу в этом порте также разделена в соответствии с приоритетами, то пакет попадает в ту очередь, которая имеет более высокий приоритет.

KS8842M имеет возможность вставлять или удалять в заголовке кадра данных для каждого выходного порта теги, определяющие приоритет в каждом индивидуальном порте выхода. Этот заголовок состоит из 2 байтов VLAN-идентификатора протокола (VPID) и 2-байтовый тег поля управляющей информации (TCI), называемый также тегом виртуальной сети VLAN по 802.1Q (рис. 13).

Вставка тега программируется в соответствующем регистре битами управления.

В порте выхода неотмеченные пакеты маркируются заданным по умолчанию тегом входного порта. KS8842M не добавляет теги к уже промаркированным пакетам.

Удаление тега программируется в соответствующем регистре битами управления. В порте выхода теги по 802.1Q VLAN из пакетов будут удалены. KS8842M не изменяет неотмеченные пакеты.

CRC повторно рассчитывается как в режиме вставки, так и в режиме удаления тегов.

Приоритетное переотображение поля

IEEE 802.1p — особенность QoS, которая позволяет KS8842M устанавливать «User Priority Ceiling» для любого входного порта. Если приоритетное поле входного пакета имеет более высокое значение, чем у заданного по умолчанию тега входного порта, то оно будет заменено приоритетным полем заданного по умолчанию тега.

Приоритет, основанный на DiffServ

Приоритет, основанный на DiffServ, использует регистры ToS, показанные в разделе Priority Control Registers [1]. Регистры управления приоритета ToS осуществляют полностью декодированный 128-битовый регистр Differentiated Services Code Point (DSCP), чтобы определить приоритет пакета из 6-битового поля ToS в заголовке IP. Когда старшие 6 битов поля ToS полностью декодированы, результирующая этих 64 возможностей сравнивается с соответствующими битами в регистре DSCP, чтобы определить приоритет.

Поддержка ограничения скорости передачи

KS8842M поддерживает аппаратное ограничение скорости передачи от 64 Кбит/с до 88 Mбит/с независимо на «получающей стороне» и на «передающей стороне» для каждого порта. Для 10-BaseT установка нормы более чем 10 Mбит/с означает, что скорость передачи не ограничена. На принимающей и передающей стороне скорость для каждого приоритета и в каждом порту может быть ограничена путем установки соответствующего значения в управляющие регистры.

Размер каждого кадра данных имеет опции, позволяющие включить минимальную межкадровую паузу— IFG (Inter Frame Gap) или байты преамбулы, в дополнение к полю данных (от пакета DA к FCS).

Для ограничения входной нагрузки

KS8842M обеспечивает возможность выборочно принимать кадры данных из всех типов кадров — групповых, широковещательных и рассылаемых в большом количестве одноадресных кадров данных.

KS8842M считает скорость приема кадров для каждого из выбранных типов кадров. Когда достигается предел скорости во входном порте, пакеты данных выбрасываются. Для ограничения нагрузки при передаче используется алгоритм «Leaky Bucket» — он применяется для каждой очереди приоритета выходных данных. Увеличенные межкадровые паузы позволяют получить равномерный выходной трафик. Производительность каждой очереди приоритета выходного порта ограничена указанной в соответствующих регистрах величиной.

Если какая-либо очередь выхода получает больше данных на передачу, чем задано, пакеты накапливаются в памяти пакетов и в очереди вывода. После того, как память для формирования очереди или память в выходном порте израсходованы, либо происходит отбрасывание пакетов, либо включается управление потоком данных.

Функция фильтрации в МАС

Cтатическая таблица в МАС используется для того, чтобы назначить определенный МАС-адрес на определенный порт. Когда одноадресный МАС-адрес не записан в статической таблице, то он также не изучается в динамической МАС-таблице. KS8842M включает опцию, которая может фильтровать или отправить одноадресные пакеты для неизвестного МАС-адреса.

Функция фильтрации одноадресных МАС-адресов полезна в случае предотвращения широковещательной рассылки одноадресных пакетов, что может ухудшить производительность этого порта в приложениях типа передачи голоса по Интернету (VoIP).

Интерфейс СППЗУ

Внешнее СППЗУ со стандартным последовательным шинным интерфейсом «microwire» используется для энергонезависимой памяти, в которой хранится информация о МАС-адресе хоста, базовом адресе, системном идентификаторе и заданных по умолчанию параметрах конфигурации (в качестве СППЗУ могут использоваться микросхемы типа 93C46 или 93C66).

Если вход разрешения EEEN установлен в высокий уровень, то KS8842M выполняет автоматическое чтение слов СППЗУ, расположенных по адресам от 0H до 6H, сразу же после снятия сигнала сброса. Значения данных из СППЗУ помещаются в определенные регистры, доступные для хоста. Операции чтения-записи СППЗУ могут также быть выполнены программным способом, путем чтения или записи в регистр EEPCR.

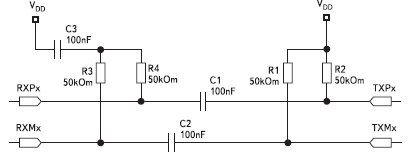

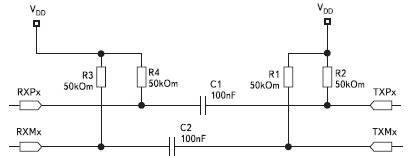

Несколько слов о системной интеграции

- Микросхему можно использовать не только для подключения к сети, но и как контроллер внутриприборного интерфейса. В таком случае развязывающие трансформаторы можно и не использовать (рис. 14, 15) [2].

Рис. 14. Варианты включения двух абонентов без согласующих трансформаторов.

Режим по переменному току

Рис. 15. Варианты включения двух абонентов без согласующих трансформаторов.

Режим по постоянному току

Такое применение микросхемы позволяет иметь единый формат сообщений во всем устройстве. При этом каждый модуль данного прибора может быть подключен к сети. Аппаратный контроль линий связи, прослушивание сообщений и другие подобные функции позволят создать надежный и удобный в разработке и эксплуатации интерфейс. Это значительно упрощает отладку модулей, облегчает программирование и сокращает время выхода на рынок готовой продукции.

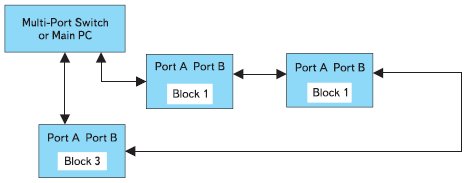

- Для небольших сетевых применений абонентов сети можно включать не по обычной схеме «все в хаб», а по последовательной цепочке (рис. 16).

Рис. 16. Вариант включения трех блоков в цепочку

Выводы

Микросхема двухканального контроллера-коммутатора Ethernet KS8842M является шагом вперед на пути, называемом «встроенный Ethernet». Кроме того, что пользователь получает возможность иметь Ethernet 10/100 Мбит/с, дополнительно предоставляется ряд важных преимуществ. К ним относятся расширенные возможности, предоставляемые коммутатором и двумя каналами Ethernet 10/100 Мбит/с. Диапазон применений микросхемы может быть достаточно широк — от контроллера-коммутатора Ethernet до контроллера внутриприборного интерфейса.

Литература

- KS8842-16/32 MQL/MVL/MQLI. 2-Port Ethernet Switch with Non-PCI Interface. Preliminary Data Sheet Rev 1.0. Micrel.

- Capacitive Coupling Ethernet Transceivers without Using Transformers. Micrel 10/100 Ethernet Products. Application Note 120. Micrel.

Иосиф КАРШЕНБОЙМ

|